Indian wins US patent for memory chips

January 4: A young IIT graduate, along with his former colleagues, recently won a US patent for designing a computer chip which enhances t...

January 4: A young IIT graduate, along with his former colleagues, recently won a US patent for designing a computer chip which enhances the memory applications in various electronic gadgets such as mobile phones and microwave ovens.

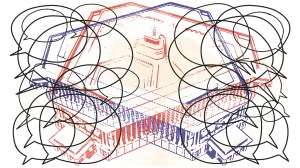

Manu Agarwal, chairman and managing director CMD of the Mumbai-based Design Expo Network Pvt Ltd won the design patent for the architecture of a row decoder for flash memory chips used in all programmable electronic devices.

8220;I had achieved the breakthrough in the flash memory chip while I was working in the US for the private firm Wafer Scale Integration as the head of the Ramp;D team. Along with my former colleages, Manek Advani and Dr K Reza, I applied for the patent rights in 1997, which were only granted now,8221; said Agarwal who has now begun his own Internet solutions and applications company in Mumbai.

The patent was granted on grounds of cost efficiency, faster accessibility and redundancy. A flash memory actually helps in retaining the memory of a gadget even if the cells or battery has been removed. For example, all the phone numbers stored in a mobile phone will not be erased in case of a power break down.

8220;Although this patent will only benefit the US firm where I was earlier working, personally I am happy that three years of my hard work have finally yielded results,8221; added Agarwal.

This is not just a personal victory for Agarwal. Other Indian techies8217; are also happy with his achievement. 8220;It was bound to happen. While the Indian software professionals have been much in demand in the US, now even the hardware engineers are much sought after in the IT world,8221; remarked the harware engineer and CEO of Vega e-Services, K Pandyan.

He added that the recent crash of dotcom companies has resulted in the spotlight being towards the deep tech8217; companies that provide a backbone to the Net infrastructure.

Agarwal graduated from IIT-Kanpur in 1992 and completed his MS in Electrical Engineering and Computer Science from the University of Minnesotta, and eventually worked on the chip architecture at Wafer Scale Integration, where he was part of a team working on future application on flash memory.

The row decoder designed by Agarwal8217;s team basically optimises the functioning of the flash memory chip along the three parametres of size, time taken for decoding and building a redundancy into the decoder.

Agarwal explained how the architecture renders the chip more efficient. 8220;We worked on reducing the size of the decoder as well as the time it takes to decode. As far as building redundancy into the chip goes, what we did was configure a row decoder that was capable of mapping the bad rows to the extra rows built into the chip,8221; he stated.

Presently, his firm is working on high end messaging solutions on the Internet. 8220;Sooner or later everybody is going to have an e-mail address in India, and hence we are working on making it more personal and accessible,8221; said Agarwal, once again proving that Indians are world leaders in Information Technology.

- 01

- 02

- 03

- 04

- 05